HDL Simulator Comparison

Sooner or later, every HDL digital engineer considers the usage of a different HDL simulator for a varienty of reasons (Compatibility, Speed, Additional Options, Language Support, Platform Support etc.). I will skip the obvious introduction of the open-source and free HDL simulators as my intention was to asses the possibilities of 2 widely used commercial simmulators this time. The QuestaBase simulator from Siemens and RivieraPRO from Aldec. Both of these support the FlexNet Licensing model on a per-year and perpetual basis.

I have been working with Modelsim/Questa for quite a while now and was really curious about the capabilities of the new Questa Base & Visualizer solution. Here I have to say that Questa Base by default allows to simulate both Verilog and VHDL files (IE Dual Language) – This is not yet a standard for Aldec, where you have to pay extra for each option.

Personally, I do not know about any HDL engineer that utilizes only one of the languages (Despite the fact that he or she codes most of the time only in one or the other language). Even myself sometimes have to deal with some 3rd party simulation libraries such as Xilinx’s FIFOs, AXI Infrastructure etc. That’s why having the ability to use only one language seems slightly dated and limited. A mixed-language simulator should be a standard in these days.

Simple Feature Comparison

RivieraPRO-LV 2024.10

- VHDL-2019 Support

- Significantly faster simulation

- User-friendly application UI

- Detailed waveform customization

- Better support and documentation

- Partial compatibility with Modelsim / Questa

- HDL Editor and Project Manager

- Missing “-skipsynthoffregion” option

- Likely Incompatibility between VIP

QuestaBase / Visualizer 2024.3

- Dual HDL language by default

- Build-In Code Coverage solution

- Can work with additional VIP IP produts from Siemens’s Portfolio

- Visualizer allows for improved experience over the old Modelsim GUI

- Also Support C-Code debugging

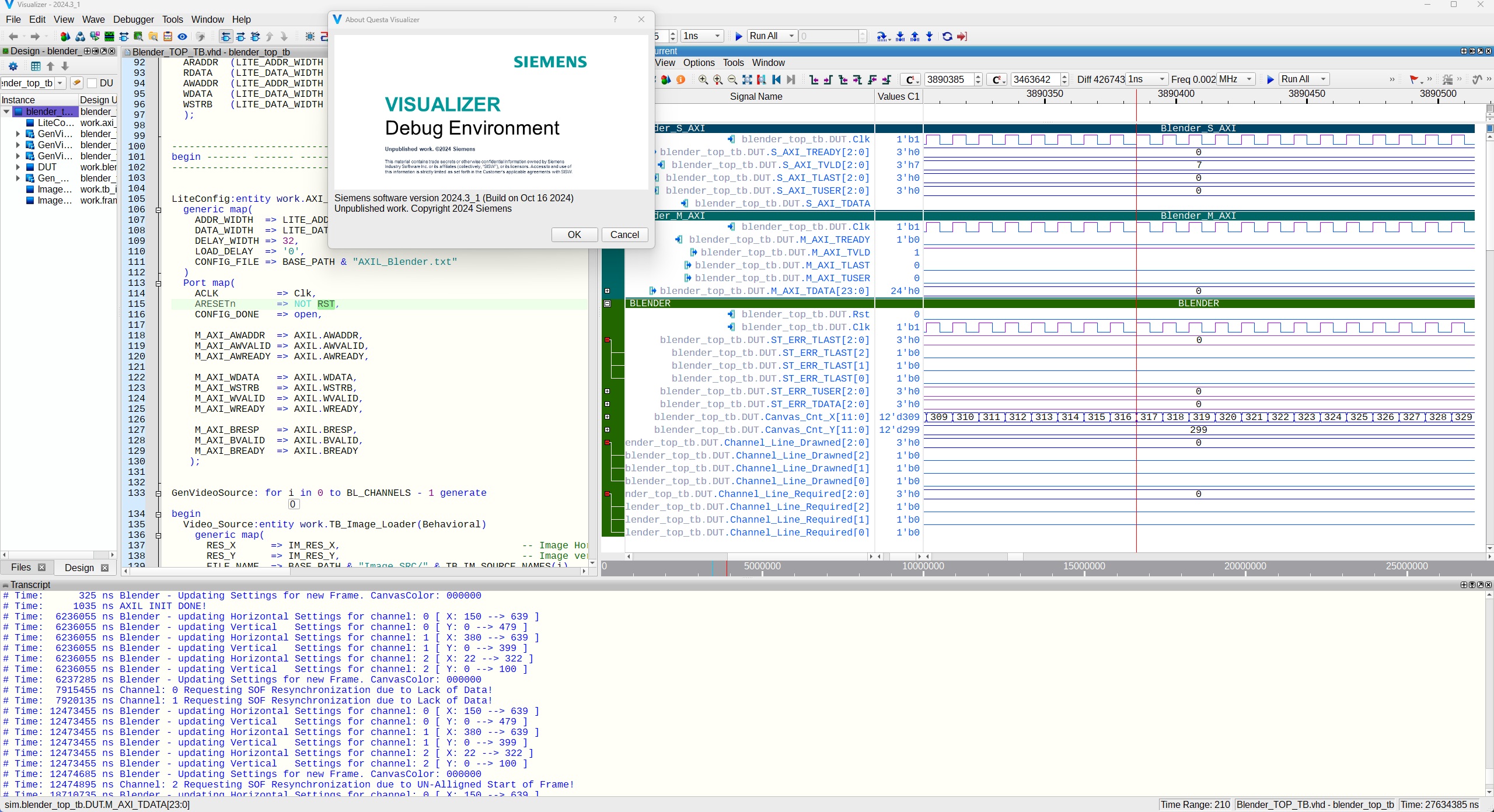

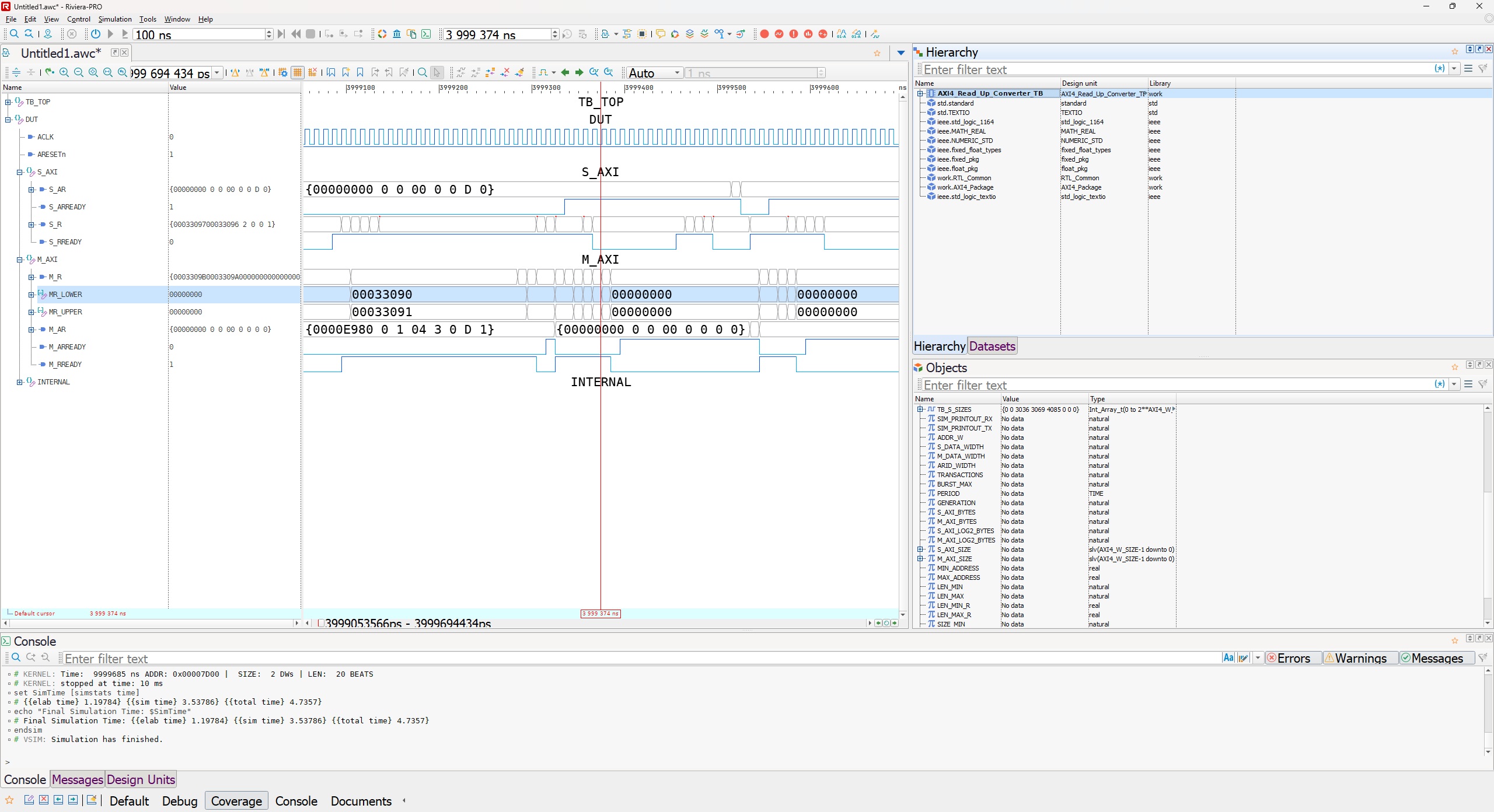

After having the ability to work with the trial version of the RivieraPRO for a couple of days, I have to admit, that it is the overall all-round winner. The new Questa Visualizer improves over the old Legacy GUI and even performance and adjustability and debugging, but it cannot yet compare with the Riviera’s pro design, elegance and simplicity in everything I tried to achieve in the tool. A great benefit for me is to adjust the waveforms to more easily see and diagnose any problems of the HDL source code, and that’s where Riviera allows for more and intuitive customizations in every detail. I also personally prefer the code coverage report generated by Riviera. Generally, comparing these 2 simulators feels a lot like Siemens’s decided to let the customer userbase rather test their products as the QuestaBase/Visualizer more looks like being still in the beta development stage despite significant improvements. As a VHDL user, the lack of support of 2019 standard in Questa Base at the beginning of 2025 is also rather somewhat unexpected and missing feature.

Because both tools are quite pricey, I was also really suprised to see that I was provided literaly zero information on the QuestaBase product. No brief, feature and speed comparison with other products or modelsim, no info on supported standards, platforms etc. In fact, eventhough I was offered the trial version of the Questa Base, I had no access to the documentaion of the Visualizer, which by the way displayed a couple of “make no sense errors (IE” Missing UVM License eventhough I do not posses any UVM-based source code)” and crashed a few times during my trial period. I have to say that I am glad that Siemens is definitely trying to improve the user experience of the Questa portfolio, however on the other hand, the Questa Visualizer is, at the time of writing, still far away from something I would call a “State-of-the-art HDL simulator solution”.

Performance & Final words

Performance was not a key factor for myself as I do mostly IP-level simulations. However I managed to do a quick comparison of performance on 2 of my “heavy duty” IPs. The FFT in Base-Radix configuration (Floating Point R2 / R4 / R8 Mixed Radix with 64K Size) and Video Blender in 3-Channel Configuration. Both designs being VHDL-2008 only. I have tested on my Laptop featuring Intel Core I7-12700H and Windows 11 Pro 24H2 version with only spotify playing in the background (Sorry). I run each of the simulations 3 times and under different configurations. The new Visualizer flow outperfromed as expected the old Questa-Base vsim flow. However in both IP cases only by about 11% and not in all configurations. IE: by 11% with no waves and no signal logging + default optimization excluding also any +acc arguments. I did also tested with the code coverage disabled in all cases. A more interesting result was while comparing the RivieraPRO performance with the QuestaBase Visualizer speed (Favoring each time the fastest among the configurations). In both cases, the RivieraPro was approx. 300% faster than QuestaBase {382 vs 128 sec for Blender and 292 vs 93 sec for FFT}. What is quite funny about this fact is that I was asking Siemens support about the performance numbers and they simply told me “If you are not happy with the speed of Questa Base, pay exxxtra for QuestaCore/Prime”😇. Overall, the support experience from Siemens’s side was rather quite sad in short.

Of course, It would be quite interesting at this time to compare the RivieraPro-LVT with the QuestaPrime speed since both versions generally offer higher speed. Eventhough I haven’t received any intel on the Questa Speed comparison, you can look it up through google to see that QuestaBase is ~25% of the Questa Core/Prime. That being said, I would assume the RivieraPRO-LVT and QuestaCore would perform with similar metrics (But thats just a rumor without no facts to back it up).

At the end of the day however, both simulators do their work just fine, so its up to your budget and the the user / company’s sales representative to decide which solution to favor. As a recent and happy “user” of the Questa VIP for PCIe, I have to admit that the Questa solution has a lot of symbiosis with other Siemens’s digital portfolio’s products – which I listed as one of the benefits of that solution. I was also quite suprised to see that same HDL code that compiles fine with Questa does not compile well Riviera (Unless you relax the LRM requirements.) – This is not a drawback though as each vendor might interpret the LRM here or there slightly different and treat some warnings as errors or the other way. The HDL Code editor and debugger in Riviera along with it’s project-based flow looks also quite comfortable and usable on the user side in comparison with the Visualizer – However I have heard that the UVM debugger is where the Visualizer really excels (Haven’t tested personally as I do not use UVM). It would be great to have the ability to compare the solutions also with the Synopsys’s FlexEDA cloud model, however, I wasn’t granted the access there as I am likely considered a “not big enough” customer. This is again where the Aldec’s support and sales representatives did an amazing job.

Clearly, both solutions offer a variety of advantages and disadvantages but for me personally, the choice was rather obvious.