AXI Data Width Convertor

Overview

The AXI4 DataWidth convertor IP converts between different bus data widths defined per the AXI4 specification. Both Upconversion and Downconversion on both Read and Write channels are supported. The convertor blocks inside the IP operate on a 4Byte (DW) boundaries, which is why the minum data width at either side is limited to 32-bit. The AXI4 transaction identification (AxID) is supported on S-AXI side in arbitrary width, however due to high design complexity and resource usage, only single ID (Single Thread) is used on M-AXI interface – thus forcing serialization of outgoing AXI transactions. The core complies to the definitions of the AxCACHE modifiable bit. When allowed to do so, the IP automatically packs all the transactions into the shortest AXI4 bursts possible. Narrow AXI4 transactions are also supported.

Features

- AXI4 Protocol Down-Conversion

- AXI4 Protocol Up-Conversion

- Write and Read Channel Support

- Narrow transfers natively supported

- VHDL 2008 RTL-based Source Code

Limitations:

- All Transactions’s addresses must be alligned to the corresppnding transaction size.

IE: Un-Alligned transactions are not supported. For example, transaction sizes of 8B must have addresses alligned to 8B.

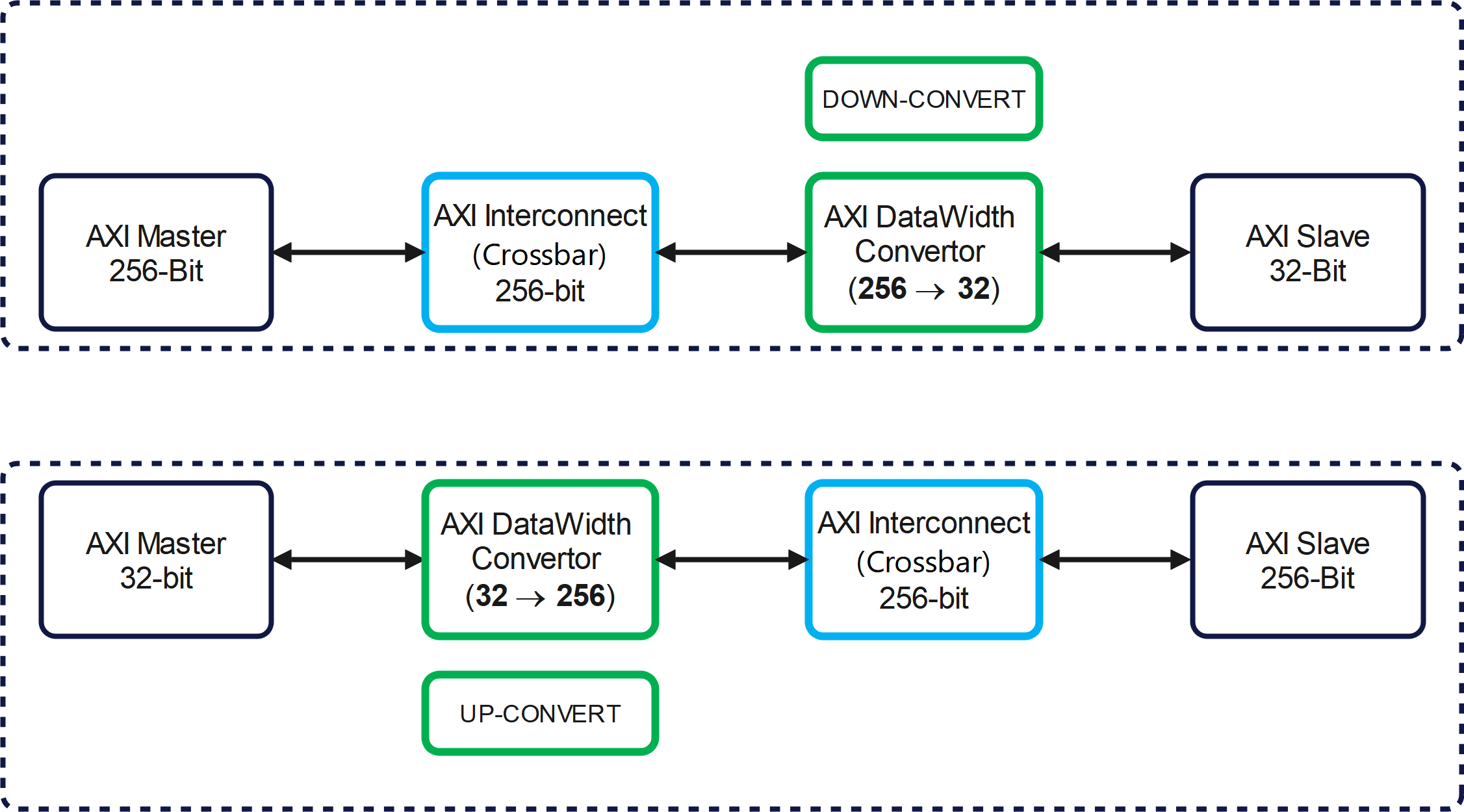

An example usage of the AXI4 datawidth Convertor around an AXI4-Interconnect in both Up and Down conversion.

NOTE: Resources and performance have been evaluated using Vivado 2024.2. Only selected configurations are shown with the default IP configuration (32-bit Addressing). The target device used for the estimates was “xcu55c-fsvh2892-2L-e” – Alveo U55C (AMD’s Ultrascale+). The tool configuration during the was were kept at the default options. Performance estimates (FMAX) are approximate and might vary across architectures, speed grades and device utilization.

Write-UpConvert - Resources and Performance

| FFs [K] | LUTs [K] | FMAX [MHz] | |

| 32:64 | 0.65 | 0.5 | 500 |

| 32:128 | 1.0 | 1.0 | 500 |

| 32:256 | 1.7 | 2.0 | 450 |

| 32:512 | 3.0 | 5.7 | 450 |

| 32:1024 | 5.8 | 15.5 | 400 |

Write-DownConvert - Resources and Performance

| FFs [K] | LUTs [K] | FMAX [MHz] | |

| 32:64 | 0.57 | 0.49 | 500 |

| 32:128 | 0.85 | 0.7 | 500 |

| 32:256 | 1.4 | 1.2 | 450 |

| 32:512 | 2.5 | 2.5 | 450 |

| 32:1024 | 4.6 | 7.6 | 400 |

Read-UpConvert - Resources and Performance

| FFs [K] | LUTs [K] | FMAX [MHz] | |

| 32:64 | 0.5 | 0.45 | 500 |

| 32:128 | 0.8 | 0.7 | 500 |

| 32:256 | 1.3 | 1.6 | 450 |

| 32:512 | 2.3 | 3.0 | 450 |

| 32:1024 | 4.4 | 6.2 | 400 |

Read-DownConvert - Resources and Performance

| FFs [K] | LUTs [K] | FMAX [MHz] | |

| 32:64 | 0.56 | 0.48 | 500 |

| 32:128 | 0.89 | 0.89 | 500 |

| 32:256 | 1.5 | 2.3 | 450 |

| 32:512 | 2.8 | 5.2 | 450 |

| 32:1024 | 5.4 | 16.16 | 400 |