AXI DMA IP

Overview

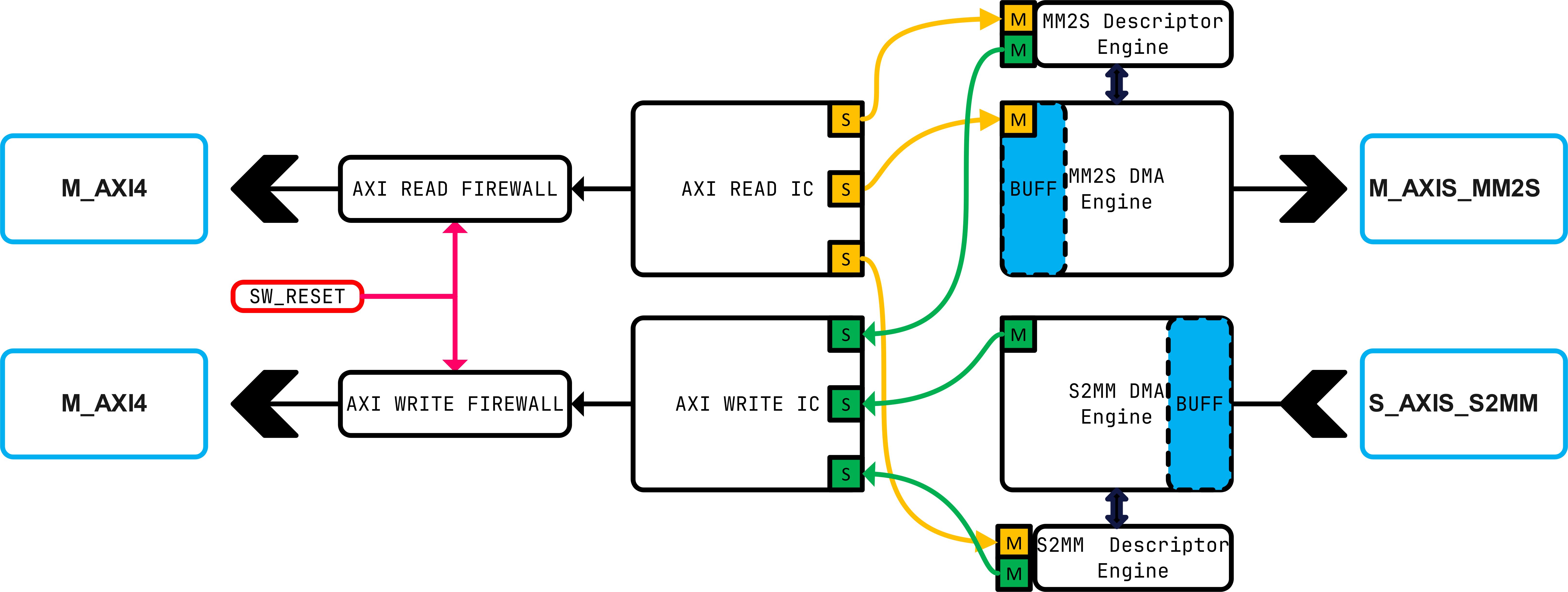

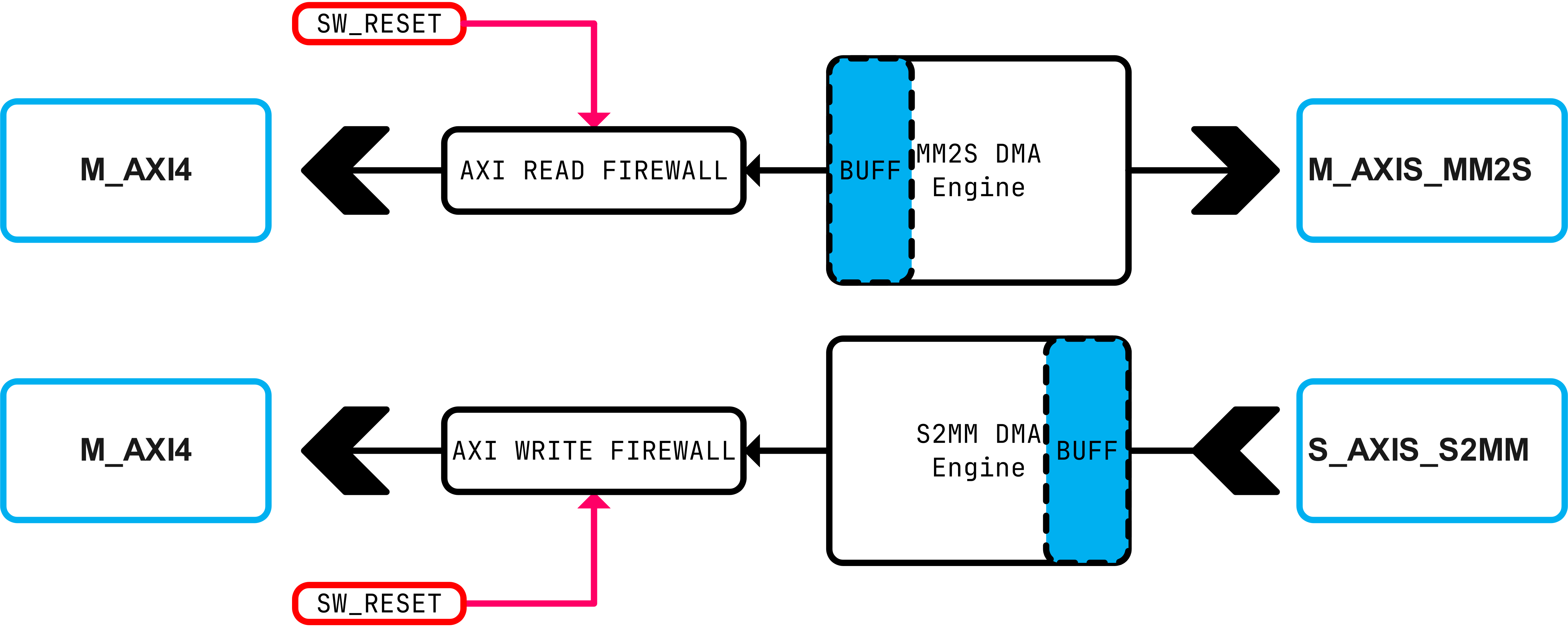

AXI DMA IP implements a generic data-mover engines on AXI4 protocol. Written from ground up in VHDL2008 standard and verified in simulator and on KCU116 hardware. It is available as a standadalone simple DMA engine (Also known as direct register DMA “Internally ZDMA”) or as a Scatter-Gather DMA engine with a predefined descriptor size of 32Bytes and build-in ECC features and engine feeedback/status stored in the descriptor.

Both of the variants supports asynchronous bidiretional transfers (S2MM and MM2S) that are AXI4-stream compliant. Included is also a software-controlled DMA Reset, which acts as an AXI4 protocol firewall that handles proper transaction closures on related AXI4 infrastructure. Due to the nature of SG engines, both directions are held in reset together. The engines supports both Interrupt and polling modes to accomodate any use case. Transfer sizes are programmed in Bytes and support transfer sizes of 4GB per single DMA transfer or per descriptor.

Features

- Build on AXI4-compliant infrastructure

- Available as Scatter-Gather DMA or simple DMA engine only

- Simple descriptor chain with feedback and error/status reporting

- Configurable maximum transfer size per descriptor / transfer up to 4GB.

- Both S2MM and MM2S Independent data streams

- MM2S: Memory-Mapped to AXI Stream (Remote Memory to AXI Stream)

- S2MM: AXI Stream to Memory-Mapped (AXI Stream to Remote Memory)

- Multiple outstanding transactions to boost performance

- Optional I/O Buffers for additional throughput enhancements

- Optional Selftest Engine for both directions

- Standard AXI4-Lite Configuration and status Interface

- Pure VHDL 2008 Vendor-Independent source code base

- Simulation and Hardware – Tested

SG-DMA Descriptor structure

typedef struct {

volatile uint32_t NEXT_DESC_LSB; // 0x00 Next Descriptor Base Address LSB

volatile uint32_t NEXT_DESC_MSB; // 0x04 Next Descriptor Base Address MSB

volatile uint32_t BUFF_LSB; // 0x08 Data Buffer Low Address

volatile uint32_t BUFF_MSB; // 0x0C Data Buffer High Address

volatile uint32_t DESC_LENGTH; // 0x10 Descriptor Length Register

volatile uint32_t DESC_CNTRL; // 0x14 Descriptor Control Register

volatile uint32_t DESC_STATUS; // 0x18 Descriptor Status Register

volatile uint32_t ECC_WORD; // 0x1C Descriptor Control (ECC) Word

}SG_Descriptor_t;

FAQ

- Does the IP supports narrow burst transfers?

No, this feature is currently not supported. - What is the Purpose of Buffering data at the I/O?

For S2MM, this makes sure that no AW transactions is sent downstream prior having the assurance of having enough data to fulfill the transaction.This might prevent for example a deadlock on the AMD’s XDMA IP in a case where the DMA is used in loopback mode.

For MM2S, having the buffer allows any AXI interconnects in between to forward the transaction data without any backpressure. This improves the performance of the interconnect,which could otherwise be stalled by the DMA engine. - How many AXI outstanding transactions are supported?

Arbitrary amount in the power-of-2 series. Note that recommended value is 4. - How many AXI Threads the IP Uses?

The IP uses a single AXI thread for communication (IE Single AXI ID).

Feel free to contact me for more details and/or additional customizations / rework to suit your design needs.

Reference linux kernel drivers and real-time PCIe performance demo can be also requested on demand.

The DMA IPs are generally optimized for performance (Both transfer rate and maximum clock rate)

Be sure to visit the DMA Demonstration for transfering video images in real time!