AXI Interconnect IP

Overview

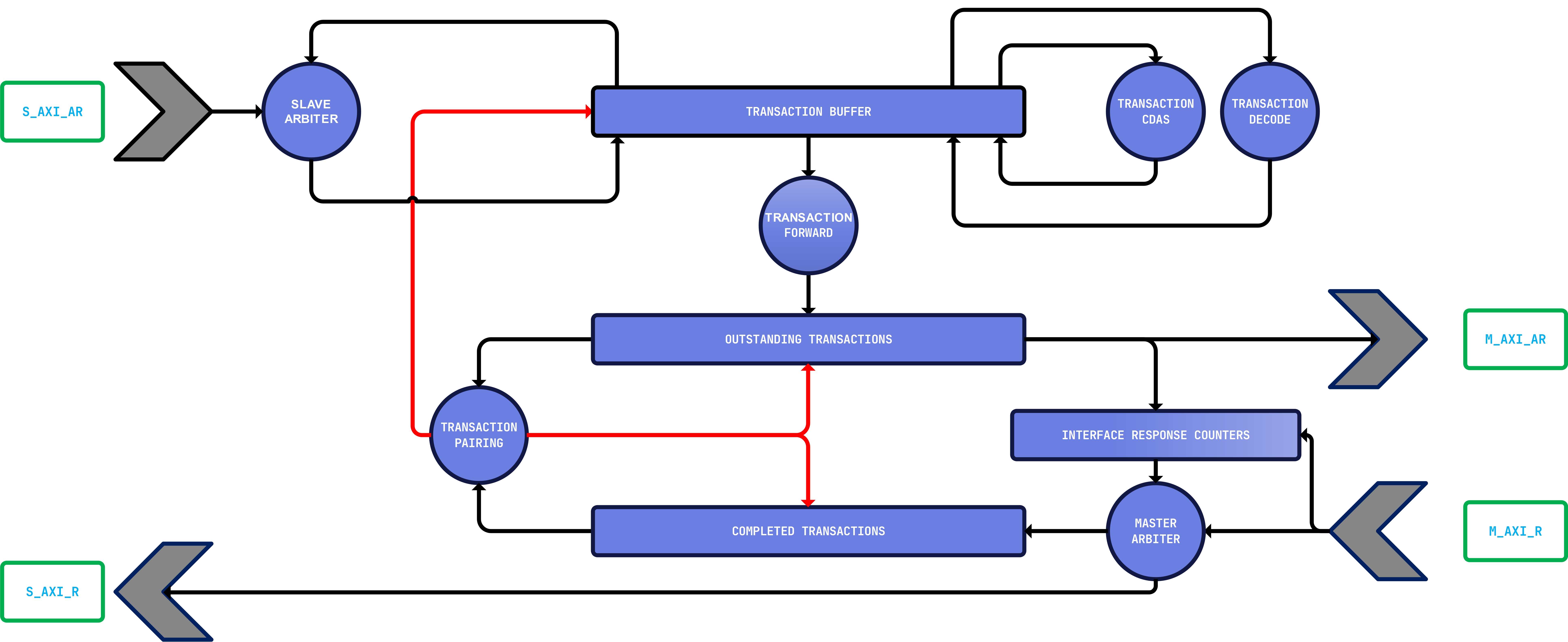

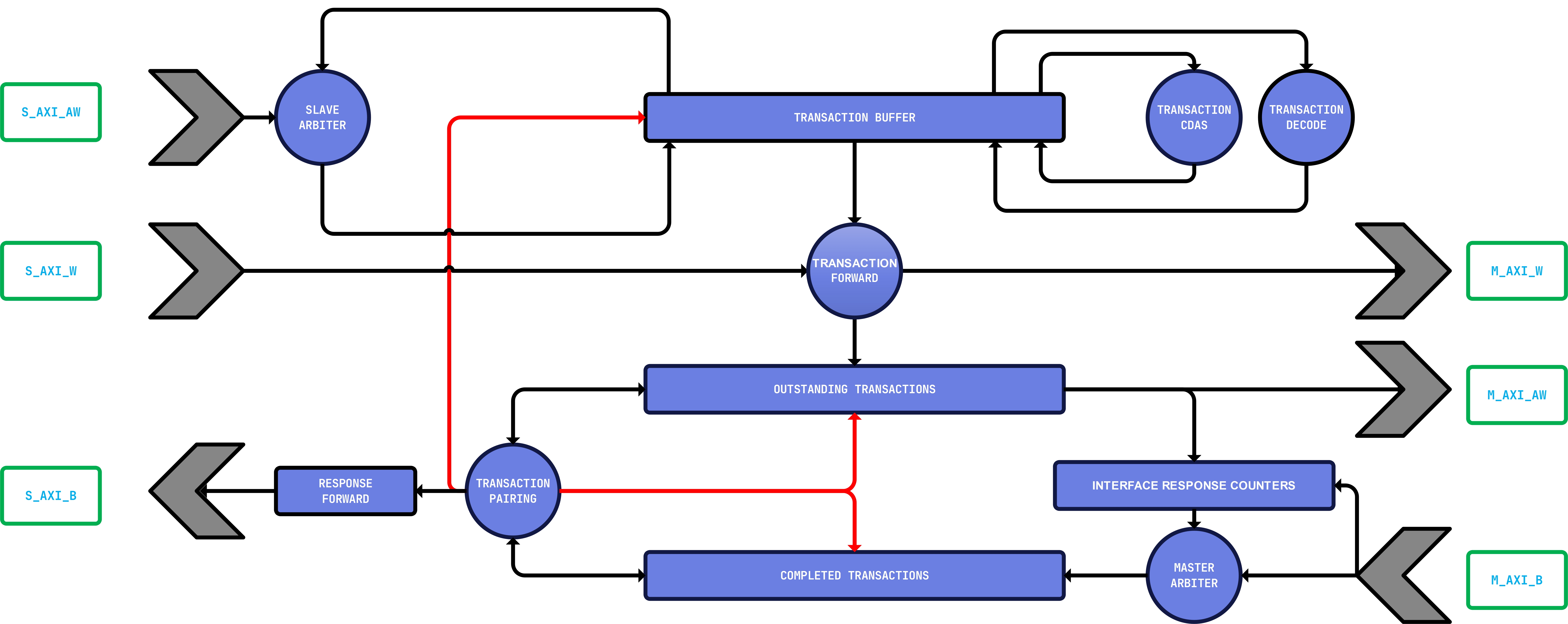

The AXI4 Interconnect IP provides a performance-optimized generic communication AXI4 crossbar switch between multiple Slave and Master interfaces (M-to-N). There is a dedicated crossbar for both AXI4-read and AXI4-write channels. Generic data, address and AXI4 identification widths are supported as well as customizable amount of outstanding AXI4 transactions (These are only limited to 2N,N ≥ 1).

The IP implements the necessary Cyclic Dependency Avoidance Schemes (CDAS) to avoid any deadlocks. Specifically, the Single Slave per active ID (SSPID) is implemented – IE a master might communicate only with a single slave with a given transaction ID. The M-to-N crossbar shares a single data route between the interfaces. Therefore, multiple masters are not allowed to communicate separately at the same time with different AXI4 slaves. In order to simplify transaction routing, the IP adds a specified amount of AXI4 ID bits on each Master interface (Both AR / AW Channels). Slave interface ID widths are intact and there is a bit-growth at the master interfaces, which is equal to ceil(log2(“IC’s Slave Interfaces”)). The build-in default AXI4 Slave makes sure that un-routable transactions do not cause any deadlocks.

Features

- AXI4 - Compliant

- Generic M-to-N crossbar Connectivity

- Multiple Outstanding Transactions

- Implements Cyclic Dependency Avoidance (CDAS) Scheme

- Default slave for handling unrouted transactions

- QoS Slave Interface Arbitration

- Generic ID / DATA / ADDR Widths

- Pure VHDL 2008 Vendor-Independent source code base

- Simulation and Hardware-Tested

FAQ

- Does the IP support data width conversion?

No, data width conversion is not supported. - Does the IP Support clock domain crossing?

No this is not supported. Any CDC must be done externally. - What is the expected throughput?

The IP is designed for performance in mind. However it is able to process one transaction in 2 clock cycles.

Therefore, using transactions with length of 1 beat will limit the performance significantly. - Which AXI Signals are not supported?

Currently, the following signals are not implemnted in the Core: AxPROT | AxCACHE | AxREGION | AxLOCK.

These can be added on demand however. - What is response signallization of the default slave?

This is DECERR (Decode Error) per the AXI4 Standard.

Feel free to contact me for more details and/or additional customizations / rework to suit your design needs.

This is a 3rd generation IP with significant design changes from the initial version that allowed for only 1 AXI Outstanding Transaction.

Be sure to checkout the realtime video blender demo that actively uses among others the AXI Interconnect solution!

AXI4 Interconnect Demonstration